|

|

От: | 4058 | |

| Дата: | 13.12.23 06:07 | ||

| Оценка: | 7 (4) +1 | ||

PD>понятно, что может быть удастся сделать технологическую норму 65 нанометров, которая даст прирост производительности процентов 30, но дальше уменьшить размер транзистора уже природа не даст.

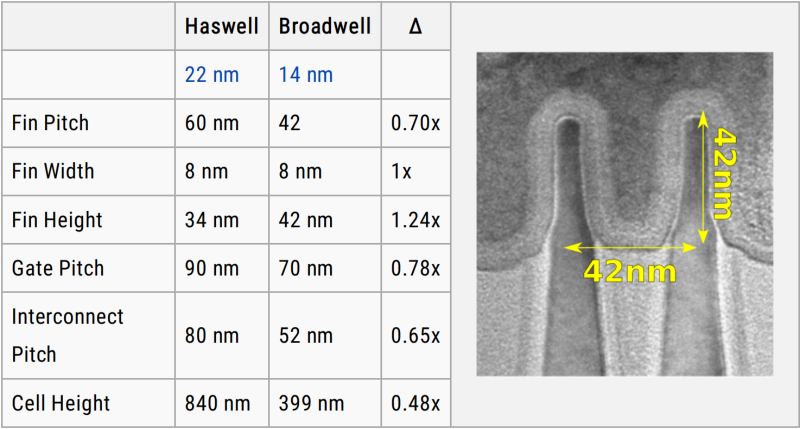

Источник: https://3dnews.ru/1071797/nanometri-v-mikroelektronikeВ транзисторах «14-нм» чипа Intel Broadwell нет ни единого элемента с характерным размером 14 нм: ширина гребней (fin width) — 8 нм, расстояние между гребнями (fin pitch) — 42 нм, высота гребней (fin height) — те же 42 нм, расстояние между затворами соседних транзисторов (gate pitch) — 70 нм, расстояние между соединительными шинами (interconnect pitch) — 52 нм, высота транзисторной ячейки (cell height) — 399 нм

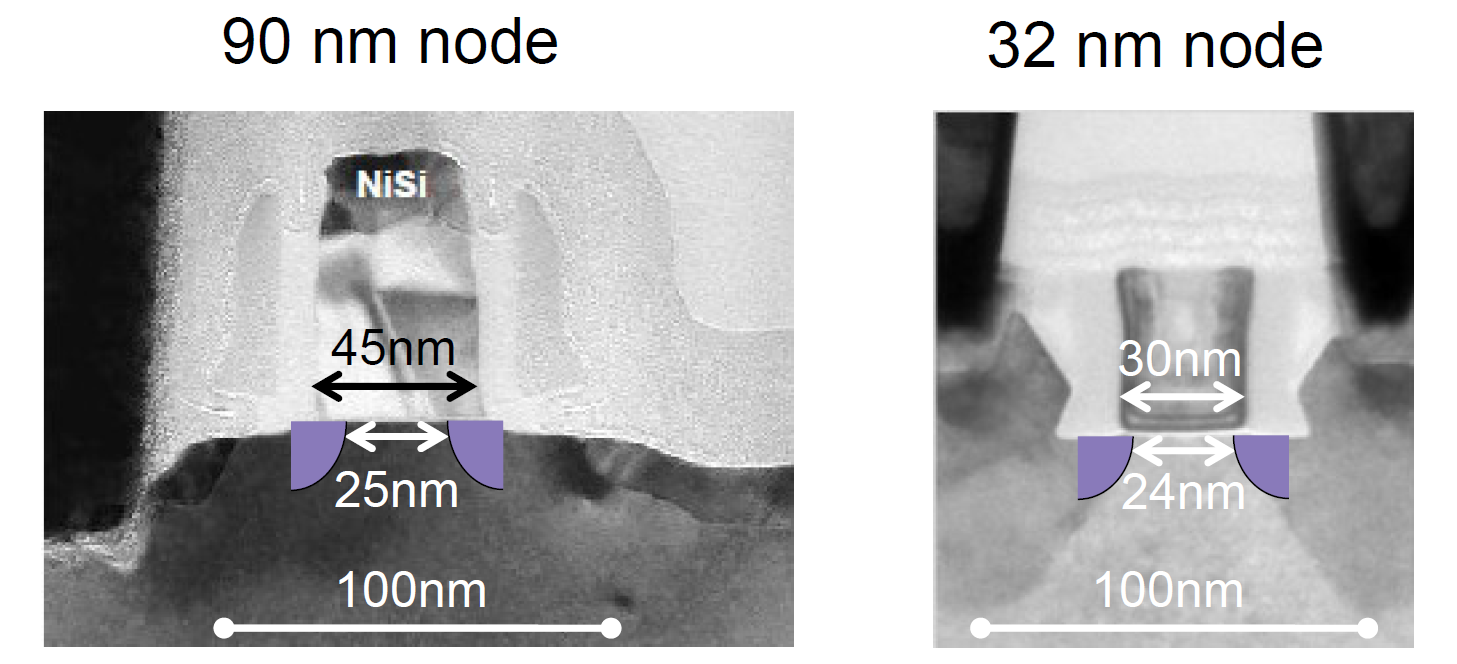

| Эффективная длина канала в технологиях 90 нм и 32 нм. | |

| |

Источник: https://habr.com/ru/articles/423575/Эффективная длина канала в технологиях 90 нм и 32 нм. Транзисторы сняты в одном и том же масштабе. Полукруги на рисунках — это форма дополнительного слабого подлегирования стоков (LDD, lightly doped drain), делаемого для уменьшения ширины pn-переходов.

...

То есть натурально “раньше у нас была длина канала 65 нм и площадь ячейки памяти Х, а теперь длина канала 54 нм, но мы ужали металлизацию, и теперь площадь ячейки стала Х/5, что примерно соответствует переходу от 65 до 28 нм. Так давайте всем скажем, что у нас проектные нормы 28 нм, а про длину канала 54 нм никому говорить не будем?” Справедливости ради, “ужали металлизацию” — это тоже важное достижение, и какое-то время после начала проблем с миниатюризацией собственно транзисторов озвученным проектным нормам соответствовала минимальная ширина металлизации, размер контакта к транзистору или еще какая-нибудь цифра на топологии. Но дальше начались пляски с FinFET транзисторами, у которых ключевые размеры никак не связаны с разрешением литографии, скорости миниатюризации транзисторов и всего остального окончательно разошлись, и единственной нормальной цифрой осталась площадь ячейки памяти, на основе которой нам сейчас и сообщают про “10”, “7” и “5” нанометров.

Источник: https://ru.wikipedia.org/wiki/5_nmТермин «5 нанометров» не имеет никакого отношения к какой-либо фактической физической характеристике (такой как длина затвора, шаг проводников или шаг затвора) транзисторов. Согласно прогнозам, содержащимся в обновлении Международной дорожной карты для устройств и систем на 2021 год, опубликованном Ассоциацией стандартов IEEE Industry Connection, ожидается, что узел длиной 5 нм будет иметь шаг контактного затвора 51 нанометр и максимально плотный шаг металла 30 нанометров. В коммерческой практике «5 нм» используется в основном как маркетинговый термин отдельными производителями микросхем для обозначения нового, улучшенного поколения кремниевых полупроводниковых чипов с точки зрения увеличения плотности транзисторов (то есть более высокой степени миниатюризации), увеличения скорости и снижения энергопотребления по сравнению с предыдущим 7-нм процессом.